本文要讨论的是半导体业,以及大部份台股投资人都很关心的晶圆代工成本,包括客户端,以及晶圆代工厂商的各项主要的成本。

我的书中有关台积电的内容

我在最近的两本书里,都讨论过台积电(美股代码:TSM)这家公司;包括了:

在《超级成长股投资法则》一书中:

- 2-4节,整个小节专门介绍介绍台积电这家公司

- 3-3节,分析科技公司的业务发展以掌握关键产业的脉动

在《10倍股法则》一书中:

- 3-2节,整个小节专门介绍包括台积电和全球的半导体供应链

客户开始出现迟疑

进入3奈米制程后,很明显地,客户对3奈米制程的采用裹足不前,不再像以往一样地抢破头。

2023年1月时传出,2022年底刚量产的台积电3奈米制程可能只有苹果一家采用,原因当然是对客户而言太过昂贵。3奈米制程使用高达25层极紫外光 (EUV) 微影曝光流程,现在每台EUV设备造价高达1.5亿到2亿美元之间,台积电为了摊平采购设备的采购成本,3奈米与后续制程不得不收取高昂费用。

另一个原因是2022年股市暴跌,全球经济衰退,企业前景不明,半导体进入每4年一次衰退的周期,所有半导体企业的存货都增加,获利下降。企业为了渡过景气寒冬,都始进行裁员,节省营运成本,大砍资本支出;这当然会影响到台积电3奈米制程的采用率。

晶圆客户的成本

流片(试生产)的成本

流片的意思就是客户把设计好的晶片,实际拿给晶圆代工厂商,按照晶圆代工厂商的实际完整的晶圆生产流程走过一遍,并实际生产几片出来。这样就可以在大量生产之前,验证是否和当初设计的功能是否完成相符。

按不同的制程工艺技术,流片的费用估计如下:

- 12奈米制程的流片费用约300万美元到500万美元的范围。

- 6奈米制程的流片费用是12奈米费用的二至三倍,大约在千万美元量级。

- 5奈米制程的流片一次需要4000万美元到5000万美元。

- 2奈米制程时,流一次片大概需要1亿美元。

晶圆代工的价码

台积电执行长魏哲家上个月表示过:「台积电的接单规模多是以 2.5 万片起跳。」

目前先进制程晶圆代工价格介于7,000~20,000美元,成熟制程晶圆代工平均价格则为3,200美元左右。视工艺制程不同,综合Center for Security and Emerging Technologies,集微网,和Digitimes的估计,每片晶圆代工的平均价格如下:

| 工艺制程 | 平均价格区间(美金)每片晶圆 |

| 3奈米 | 20000+ |

| 4奈米 | 18000-20000 |

| 5奈米 | 16000 |

| 7奈米 | 10000 |

| 16奈米和12奈米 | 5000 |

| 28奈米 | 3000 |

代工商方面

晶圆代工的成本

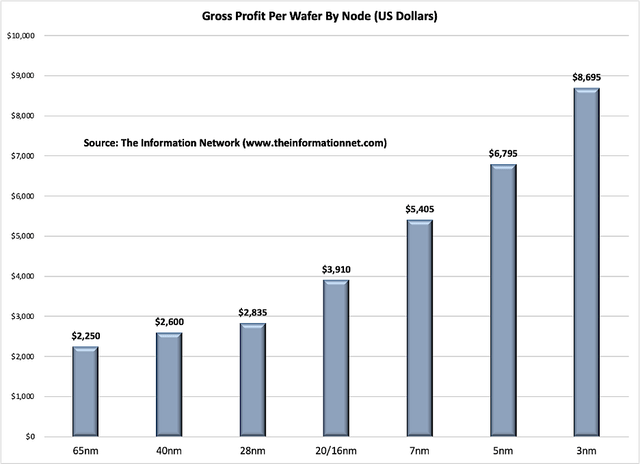

下面这张图是The Information Network所提供,视工艺制程不同,每片晶圆制造的毛利比较图。

晶圆代工研发成本

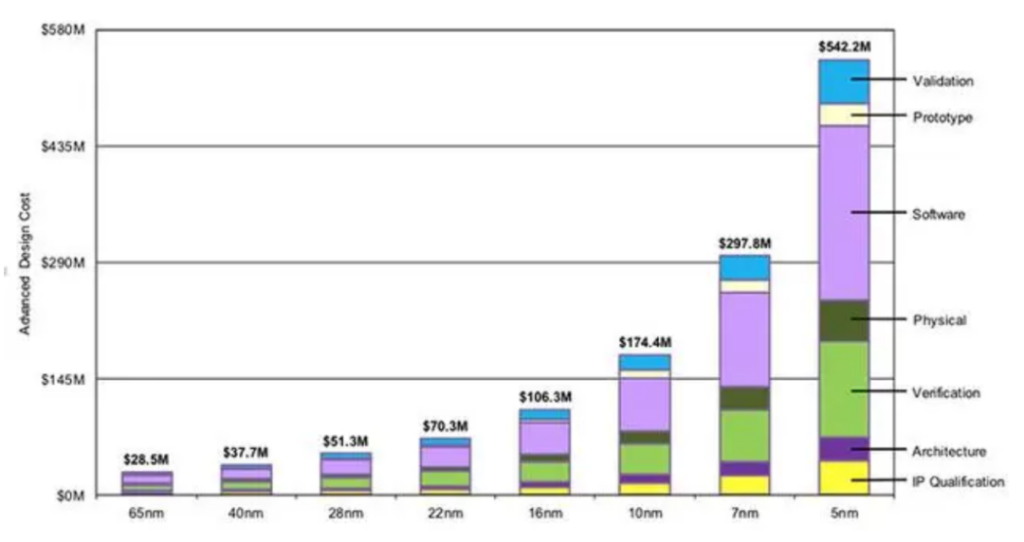

从先进工艺设计成本来看,根据第三方半导体研究机构Semi engineering计算,28奈米米制程的开发费用大约为5130万美元,到16奈米制程需要投入1亿美元,到5奈米制程节点,这个费用达到5.42亿美元。如果按照接近两倍涨幅测算,在2奈米制程上,开发费用可能会将近20亿美元。这个费用包括了IP授权、软体、确认、验证、架构等环节。

图片来源:Semi engineering

晶片工厂的建厂成本

第三方分析机构IBS测算过晶圆厂在先进工艺的研发投入,3奈米制程的工艺研发投入达到40亿美元-50亿美元,建一座3奈米制程、每月生产4万片的生产线,成本约为150亿美元-200亿美元。

因此美国今年所通过的晶片法案所编列的540亿美,听起来是很大的天文数字。但一间先进制程的晶片制造厂需要上百亿美金。读者就可以知道,这对美国已落后亚洲廿年的晶片制造,基本上根本起不了大作用,象征性意义大于实质作用。

供应链相关厂商的投入

研发所需的时程

晶片制造工艺的技术从研发到实验室,通常是一个非常漫长和耗费各项资源(包括人力,资本,设备,软体,材料各个环节缺一不可)的过程,往往需要7年-10年的时间。以2奈米制程的技术路线为例;在半导体业界,2016年的时候就已经很明确了,而在2014年左右,已经有研究论文发表。

到今年,三大半导体制造商台积电,三星,英特尔才初步能估计试产的推出时程,可见需要多大的资源持续的投入。这就是摩尔定律的残酷所在,一旦跟不上某一个晶片制造工艺的技术的节点,就很可能就永远被甩在后面,往后再想追上所要花的力气,会远超出所有人能想像的。

供应商扮演的角色

晶片供应链最关键的有三类厂商;包括设备,软体(主要是IP和EDA),材料。

先进制程越往下走,光罩张数及工艺复杂度都显著升高,良率的提升就越难。这不仅考验设计企业、考验代工厂,也考验设备厂商。基于良率,IP及对应完备工艺设计生态的考虑,在选择工艺架构时,厂商都非常慎重,非必要不会更换。

全新的工艺架构,背后是庞大的工程。涉及到设备的更换,机台的更换又涉及到成本、良率以及与新工艺架构生态的建立。台积电在进行新工艺架构的制程开发,机台的更换的比率尽可能不会超过10%,这样能够保证生产的良率。另一个巨大的工程是,IP需要重新搭建,重新验证,这对代工厂和设计公司而言重新搭建新的工艺生态无疑的存在诸多不确定性。

关键环节

光刻机

请参考我之前写的另一篇部落格文章《真正掐住台积电脖子的企业艾司摩尔(ASML)》

EDA

主要的EDA厂商新思科技(美股代码:SNPS)的主流工具是以9个月为固定周期进行版本的更新。EDA工具的更新和迭代分为两种,一种是演进式,这是最主要的发展方式,主要是根据工艺、应用等新的特点和需求对现有工具进行功能增强,这种迭代是持续进行中的。

另一种EDA工具的发展是革命性的,通过推出革命性的工具和方法学,引领业界发展方向的创新。

几年前,新思科技就和代工厂一起研发2奈米工艺的EDA工具,在代工厂接下新客户之前,他们会拿着新思科技的EDA工具不断进行验证,直到最后通过。很多研究都是并行的,不是说研发出了3奈米之后,才开始研发2奈米。

先进制程晶片的成本迅速暴增,7奈米晶片设计成本为3.49亿美元,而5奈米晶片设计成本将增至4.76亿美元,企业都在设计开发先进制程晶片,使得购买EDA工具以及支付授权费直线增加。

结论

2奈米制程才刚开始,关于1.5奈米制程的讨论已经在半导体的技术讨论会上开始,2025年之后,将会出现一个新的架构,业界称之为FortSheet,到了2030年,又有新的结构被讨论出来,并可能成为现实。摩尔定律会放缓,但可能会一直延续。

相关文章

- 《台积电目前和未来共有多少晶圆厂和封装测试厂?》

- 《目前获利丰厚的五大人工智慧商》

- 《台积电的DCF内在价值是多少?如何用免费工具程式快速地计算出来?》

- 《台积电,三星,英特尔良率和先进制程的比较》

- 《台积电晶圆代工的成本,价码,研发成本》

- 《台积电,英特尔,三星未来晶片的新制程路线图对照》

- 《真正掐住台积电脖子的企业艾司摩尔(ASML)》

- 《为何台积电的利润率远大于竞争对手?》

- 《台积电(TSMC)的2大长期威胁:美国和中芯》

- 《台积电眼前的几大挑战》

- 《台积电负面的企业文化和管理方式不利未来和成长》

- 《台积电如何赚钱?》

- 《Zyvex和次奈米半导体制程的目前发展,会威胁到台积电吗?》

- 《台积电眼前的几大挑战》

- 《英特尔是怎么赚钱的?以及投资它的好处 》

- 《英特尔目前艰难的困境》

- 《德州仪器(Texas Instruments)如何赚钱?惊人的长期资本回报和公司净利润率!》

- 《超微(AMD)如何赚钱?企业史上罕见的反败为胜案例》

- 《长年老二的超微(AMD)表现为何令人瞠目结舌?》

- 《高通(Qualcomm)多元化成功,已不再只靠手机赚钱》

- 《辉达(nVidia) 如何赚钱?辉达改变了产业的游戏规则 》

- 《博通(Broadcom)如何赚钱?经营方式的1项重大改变》

- 《无所不在的安谋(Arm)如何赚钱?》

- 《什么是第三代半导体》

- 《半导体设备之王应用材料(Applied Materials)是如何赚钱的?》

- 《常见的6大半导体投资迷思》

- 《利润丰厚的半导体供应链》

- 《细论全球半导体晶片市场,9大细项分析》

- 《资料中心是仍在高速成长的半导体领域》

- 《2024年迄今,四家半导体企业在标普500的涨幅中贡献了三分之一》

- 《目前获利丰厚的五大人工智慧商》

- 《EDA寡占商:益华(Cadence)如何赚钱?》

- 《EDA寡占商:新思(Synopsis)如何赚钱?》

- 《三大EDA寡占商:新思(Synopsys),益华(Cadence),⻄⾨⼦(Mentor Graphics)》

重要声明

- 本站内容为作者个人意见,仅供参考,本人不对文章内容、资料之正确性、看法、与即时性负任何责任,读者请务必自行判断。

- 对于读者直接或间接依赖并参考本站资讯后,采取任何投资行为所导致之直接或间接损失,或因此产生之一切责任,本人均不负任何损害赔偿及其他法律上之责任。